#### ELECTRICAL AND COMPUTER ENGINEERING DEPARTMENT, OAKLAND UNIVERSITY ECE-2700: Digital Logic Design

### **Student Honor Pledge:**

All work submitted is completed by me directly without the use of any unauthorized resources or assistance Initials:

# uiz 3 (November 9<sup>th</sup> @ 5:30 pm)

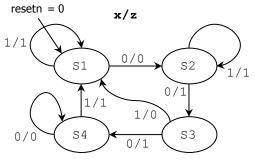

## PROBLEM 1 (30 PTS)

• Complete the timing diagram of the following state machine:

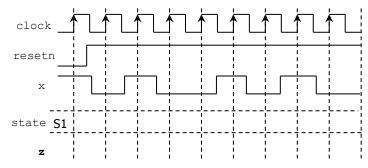

## PROBLEM 2 (30 PTS)

• Complete the timing diagram of the circuit whose VHDL description is shown below:

signal qt: std logic; begin process (rstn, clk, a, b, x) begin if rstn = '0' then qt <= '0'; elsif (clk'event and clk = '1') then if x = 11' then qt <= qt xor (a xor b); end if; end if; end process; q <= qt;

end xst;

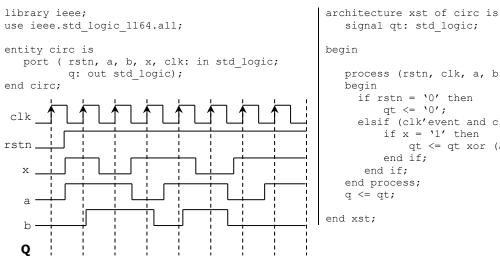

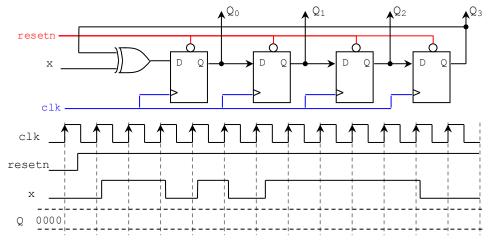

# PROBLEM 3 (40 PTS)

• Complete the timing diagram of the following circuit.  $Q = Q_3 Q_2 Q_1 Q_0$

Get the excitation equation for  $Q_0$  (5 pts).